# REHDESIGN

# IDE-Interface

Manual

# 1. Einführung

Das REHDESIGN IDE-Interface ist eine Peripheriebaugruppe im Europaformat zur Verwendung in ECB-Bus-basierenden Mikrocomputersystemen. Die Baugruppe umfaßt neben dem namensgebenden Interface zum Anschluß von IDE- (AT-Bus) Festplatten eine aktive Terminierung für alle Signale des ECB-Bus, eine parallele Druckerschnittstelle (Centronics) sowie eine Schaltung zum manuellen Auslösen von Reset und NMI. Damit dient das IDE-Interface in erster Linie als sinnvolle Ergänzung von Single-Board-Computern wie z.B. der REHDESIGN CPU280, es kann aber an allen ECB-Bus-Systemen verwendet werden.

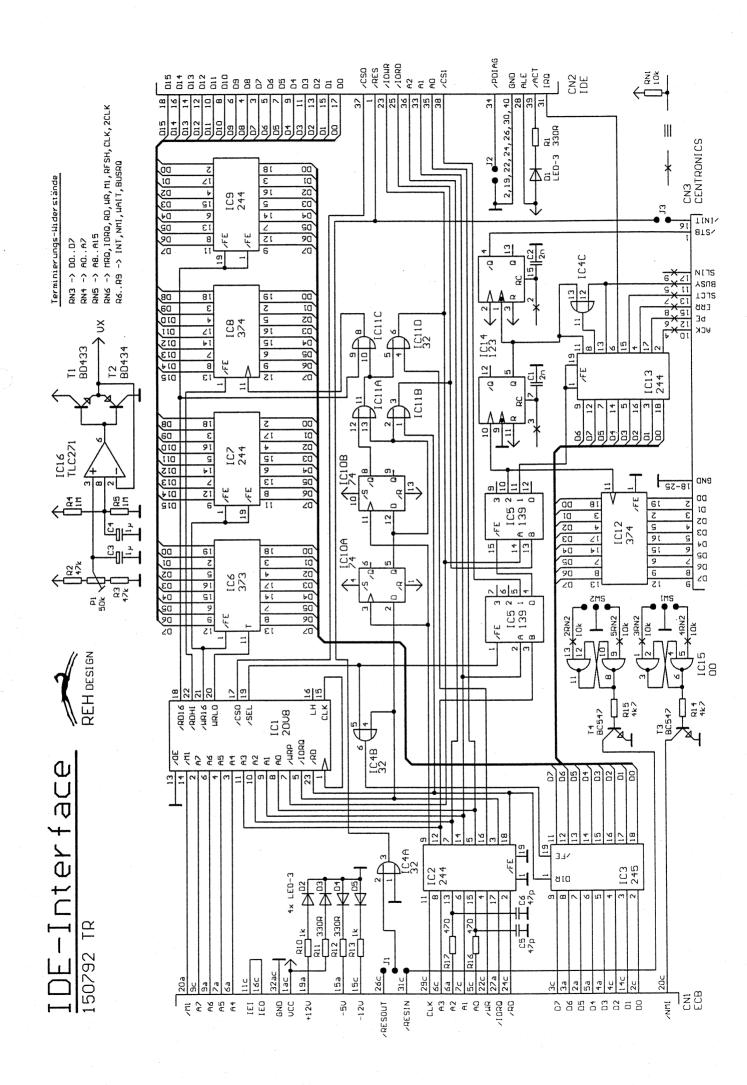

# 2. Schaltungstechnisches

Die Schaltungsteile Busterminierung, Centronics-Interface und Reset/NMI sind einfach, wenn nicht gar primitiv, zu realisieren. Zum Anschluß einer IDE-Festplatte hingegen ist ein gewisser Schaltungsaufwand unvermeidbar, will man nicht erhebliche Umstände bei der Software in Kauf nehmen. Festplatten mit IDE-Interface übertragen die Nutzdaten in Worten zu 16 Bit, während ein Zugriff vom ECB-Bus-Master jeweils nur ein Byte (8 Bit) übertragen kann. Deswegen müssen die 16-Bit-Daten auf zwei verschiedene 8-Bit-Zugriffe aufgeteilt werden. Die schaltungstechnisch einfachste Möglichkeit wäre das Aufteilen auf zwei I/O-Adressen, so daß die beiden Wort-Hälften an der Adresse unterschieden werden können. Diese Technik läßt jedoch keinen DMA-Betrieb zu, denn DMA-Controller können nicht immer abwechselnd auf zwei verschiedene Adressen zugreifen. Beim hier beschriebenen Interface wird daher ein anderer Weg beschritten: die Unterscheidung erfolgt durch die Reihenfolge der Zugriffe, d.h. Zugriffe auf dieselbe I/O-Adresse werden immer abwechselnd den beiden Worthälften zugeordnet. Dazu wird intern ein Flip-Flop bei jedem Zugriff gekippt. Diese Aufteilung von 16-Bit-Worten in zwei einzelne Bytes darf jedoch nur bei Datenzu-griffen erfolgen, da sämtliche Steuerregister der IDE-Festplatte nur 8 Bit breit sind. Durch das Rücksetzen des Flip-Flops bei Zugriffen auf die Steuerregister wird erreicht, daß jeweils beim Beginn eines Datentransfers ein definierter Zustand vor-

Fast die gesamte Adreßdekodierung und die Wort-Aufteilung wird mit einem GAL realisiert. Die restlichen Funktionen übernehmen einfache TTL-Bausteine. Dadurch bleibt die Schaltung übersichtlich und der Kostenaufwand gering.

Beim I/O-Timing des ECB-Bus gibt es ein zeitkritisches Detail: Beim Schreiben von Daten zur Peripherie werden die Daten fast gleichzeitig mit den Strobe-Signalen ungültig. Im Zusammenspiel mit den (recht großen) von IDE-Festplatten geforderten "Data Hold Times" ergibt sich ein echtes Problem. Beim IDE-Interface wird daher etwa in der Mitte des Zugriffes mit IC10 und IC11 synchron ein Schreibimpuls erzeugt, nach dem die Daten hinreichend lange gültig bleiben. Dieser Schreibimpuls wird sowohl zur Ansteuerung der IDE-Festplatte als auch zum Speichern der Centronics-Daten genutzt. Darüberhinaus sorgt ein entsprechender Puls für ein sicheres Übernehmen der höherwertigen Worthälfte beim Lesen von IDE-Daten.

Ein weiterer Schwachpunkt bei der Verwendung von IDE-Festplatten liegt im relativ labilen Interface-Verhalten dieser Laufwerke. So reagieren diese Geräte äußerst sensibel auf kurze Impulse (Spikes) auf den Adreßleitungen, selbst wenn diese Impulse ausreichenden zeitlichen Abstand zu gültigen Zugriffen haben. Im zur Entwicklung verwendeten ECB-System verursachte das Einschalten des Datenbus beim Aktivieren des Signals /IORQ ebensolche Impulse auf den (unmittelbar neben dem Datenbus liegenden) Adreßleitungen A0 und A2, was die angeschlossene Festplatte völlig durcheinander brachte. Die einzige wirklich sichere Möglichkeit zur Korrektur scheint im Einbau entsprechender Zeitkonstanten zu liegen - hier realisiert durch R16, R17, C5 und C6. Durch diese RC-Tiefpässe werden Spikes hinreichend gedämpft, um hinter dem Eingangstreiber nicht mehr aufzutauchen; die entstehende Signalverzögerung hat keine störenden Auswirkungen.

# 3. Stückliste

| IC1 IC2,IC7,IC9,IC13 IC3 IC4,IC11 IC5 IC6 IC8,IC12 IC10 IC14 IC15 IC16 |                                                          | GAL 20 V 8, 25 ns oder schneller<br>74 HCT 244<br>74 ACT 245 (oder ALS)<br>74 HCT 32<br>74 HCT 139<br>74 HCT 373<br>74 HCT 374<br>74 HCT 74<br>74 HCT 123<br>74 HCT 00<br>TLC 271 |  |  |

|------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| T1                                                                     |                                                          | BD 433                                                                                                                                                                            |  |  |

| T2                                                                     |                                                          | BD 434                                                                                                                                                                            |  |  |

| T3,T4                                                                  |                                                          | BC 547 o.ä.                                                                                                                                                                       |  |  |

| D1,D2,D3,D4,D5                                                         |                                                          | LED 3mm rot o.ä.                                                                                                                                                                  |  |  |

| C1,C2                                                                  |                                                          | 2 n 2 ker. RM 5                                                                                                                                                                   |  |  |

| C3,C4                                                                  |                                                          | 1 μ Ta. RM 2.5                                                                                                                                                                    |  |  |

| C5,C6                                                                  |                                                          | 47 p ker. RM 5                                                                                                                                                                    |  |  |

| CK1-16,CK19-20                                                         |                                                          | 18x 100 n ker. RM 5                                                                                                                                                               |  |  |

| CK17,CK18                                                              |                                                          | 10 μ Ta. RM 2.5                                                                                                                                                                   |  |  |

| R1,R11,R12                                                             |                                                          | 330 R                                                                                                                                                                             |  |  |

| R2,R3                                                                  |                                                          | 47 k                                                                                                                                                                              |  |  |

| R4,R5                                                                  |                                                          | 1 M                                                                                                                                                                               |  |  |

| R6,R7,R8,R9                                                            |                                                          | für Terminierung Spezialsignale                                                                                                                                                   |  |  |

| R10,R13                                                                |                                                          | 1 k                                                                                                                                                                               |  |  |

| R14,R15                                                                |                                                          | 4 k 7                                                                                                                                                                             |  |  |

| R16,R17                                                                |                                                          | 470 R                                                                                                                                                                             |  |  |

| P1                                                                     |                                                          | 50 k (Trimmer 10mm liegend)                                                                                                                                                       |  |  |

| RN1                                                                    |                                                          | RSIL 8x 10k                                                                                                                                                                       |  |  |

| RN2                                                                    |                                                          | RSIL 4x 10k                                                                                                                                                                       |  |  |

| RN3-6                                                                  |                                                          | 4x RSIL 8x, für Term. (220-330 R)                                                                                                                                                 |  |  |

| CN3a<br>J1                                                             | ECB<br>IDE<br>CENTR.<br>CENTR.<br>RESET<br>PDIAG<br>INIT | VG-Leiste 64-pol. ac<br>Pfosten 40-pol.<br>DB 25 S 90°<br>Pfosten 26-pol (wahlw. CN3/CN3a)<br>Pfosten 1x3<br>Pfosten 1x2<br>Pfosten 1x2                                           |  |  |

# 4. Einstellungen

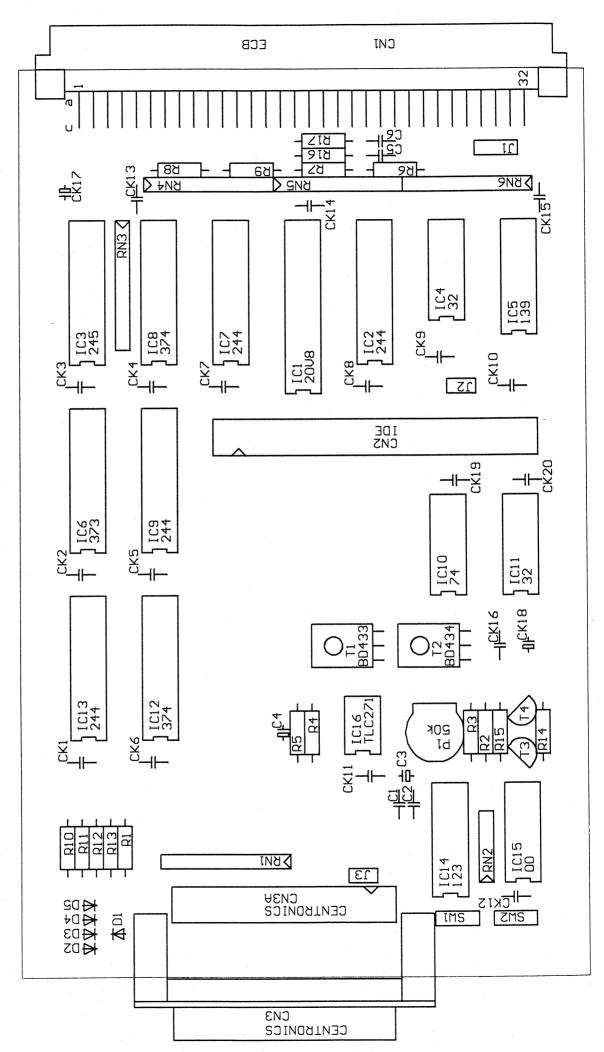

Als Steckverbinder für die Centronics-Schnittstelle kann wahlweise ein abgewinkelter Sub-D-Stecker (für Einschubsysteme mit Frontplatten) oder ein Pfostenstecker (zum Herausführen an eine beliebige Steckerposition) bestückt werden.

Vor der Inbetriebnahme ist die Terminierungsspannung einzustellen, auch müssen die Jumper entsprechend der gewünschten Eigenschaften gesetzt werden.

Als Spannung für die aktive Terminierung hat sich ein Wert von 2,6 bis 2.7 Volt gut bewährt. Diese Spannung bietet ausreichende Last (und damit Dämpfung) sowohl für High- als auch für Low-Signale. Für die Widerstandsarrays sind Werte von 220 bis 330 Ohm empfehlenswert (sollte etwa dem Wellenwiderstand der Busplatine entsprechen). Bei Verwendung der CPU280 als Busmaster ist die Bestückung der Einzelwiderstände R6 bis R9 normalerweise nicht erforderlich.

Jumper J1 (Reset) wird üblicherweise in die "obere" Position gebracht, so daß das Bus-Signal "Reset-Out" (26c) zur Platte weitergereicht wird.

Jumper J2 bleibt normalerweise offen (nur für Testzwecke). Jumper J3 ist ebenfalls im Normalfall offenzulassen (wer will schon bei einem Rechner-Reset auch den Drucker rücksetzen?).

# 5. Programmierung des GAL's

Mit einem GAL des Typs 20V8 (IC1) sind alle zentralen Funktionen des IDE-Interface realisiert.

TITLE AUTHOR IDE/CENTRONICS INTERFACE GAL IC1

AUTHOR TILMANN REH

COMPANY REHDESIGN

DATE 08.06.1992

; Zugriffe auf die Festplatte erfolgen immer bei LH = High. Dadurch hat ; dieses Signal beim Lesen die gegenteilige Bedeutung wie beim Schreiben. ; Damit der erste Lesezugriff die Platte anspricht, muß vor dem eigentlichen ; Datentransfer einmal das Datenregister gelesen (LH gesetzt) werden.

#### CHIP IDE PAI CE 20V8

CK A7 A4 A5 IORQ A6 WRP A0 A1 A2 A3 GND OE M1 CLK LH CS0 RD16 SEL WRLO WR16 RDHI RD VCC

; Basisadresse nur hier (BASE) ändemi Low-Nibble der Adressen tellweise ; durch Hardware festgelegt und nicht veränderbar.

STRING BASE '(A7 \* /A6 \* /A5 \* /A4)'

: Basisadresse 80h

STRING PARSEL '(BASE \* /A3 \* A2 \* /A1 \* A0)'

STRING CS1ADR '(BASE \* /A3 \* A2 \* A1)'

STRING DATADR '(BASE \* A3 \* /A2 \* /A1 \* /A0)'

STRING TFRADR '(BASE \* A3 \* (A2 + A1 + A0))'

STRING IDEADR '(CS1ADR + DATADR + TFRADR)'

STRING IO '(/IORQ \* M1)'

; Centronks Adr. x5 ; CS1 Adr. x6..x7 ; CS0/Daten Adr. x8 ; CS0/Task Adr. x9..xF ; alle IDE-Adressen ; I/O-Request

: Data MSB aus Latch lesen

## **EQUATIONS**

| /CSO  | = TFRADR<br>+ DATADR * LH                                     | ; Task File Zugriff<br>; Data Write MSB / Read LSB              |

|-------|---------------------------------------------------------------|-----------------------------------------------------------------|

| /SEL  | = (PARSEL + IDEADR) * M1                                      | ; Kartenzugriff (nur Adr.!)                                     |

| /CLK  | = (DATADR + TFRADR) * IO                                      | ; LH-Takt: Data & Task File                                     |

| LH    | := /LH * /TFRADR                                              | ; FilpFlop: LSB/MSB Toggle<br>; Reset bel Task File Zugriff     |

| WRLO  | = DATADR ' IO ' /WRP ' /LH<br>+ (TFRADR + CS1ADR) ' IO ' /WRP | ; Data LSB in Latch schreiben<br>; Transparent für alle anderen |

| /WR16 | = IDEADR * IO * RD                                            | ; MSB und latched LSB zum IDE                                   |

| /RD16 | = DATADR * IO * /RD * LH<br>+ (TFRADR + CS1ADR) * IO * /RD    | ; Data LSB lesen, MSB latchen<br>; alle anderen transparent     |

|       |                                                               |                                                                 |

# 6. Belegung ECB-Bus

/RDHI = DATADR \* !O \* /RD \* /LH

| a        | Nr     | c       |

|----------|--------|---------|

| +5V      | 1      | +5V     |

| D5       | 2      | D0      |

| D6       | 3<br>4 | D7      |

| D3       | 4      | D2      |

| D4       | 5      | A0      |

| A2       | 6      | A3      |

| A4       | 7      | A1      |

| A5       | 8      | A8      |

| A6       | 9      | A7      |

| /WAIT    | 10     |         |

| /BUSREQ  | 11     | IEI     |

|          | 12     |         |

| (+12 V)  | 13     |         |

|          | 14     | • D1    |

| -5 V     | 15     | -12 V   |

| 2xCLK    | 16     | IEO     |

|          | 17     | A11     |

| A14      | 18     | A10     |

| +12 V    | 19     |         |

| /M1      | 20     | /NMI    |

|          | 21     | /INT    |

|          | 22     | /WR     |

|          | 23     |         |

|          | 24     | /RD     |

|          | 25     | (/HALT) |

| gono.    | 26     | /RESOUT |

| /IORQ    | 27     | A12     |

| /RFSH    | 28     | A15     |

| A13      | 29     | CLK     |

| A9       | 30     | /MRQ    |

| (/BUSAK) | 31     | /RESIN  |

| GND      | 32     | GND     |

# 7. Software

Das IDE-Interface belegt insgesamt 11 Adressen im I/O-Adreßraum des ECB-Bus. Dabei kann die Basisadresse durch entsprechende Programmierung in 16er Schritten frei gewählt werden, während die unteren 4 Bit der Adressen nicht geändert werden dürfen. Es werden immer die Adressen x5h bis xFh belegt, bei der Standardprogrammierung des GAL also 85h bis 8Fh. Die einzelnen Ports liegen auf folgenden Adressen (bei Basisadresse 80h):

## 85h Centronics-Port

Schreibzugriffe auf diese Adresse geben das entsprechende Zeichen auf die Schnittstelle aus (8 Bit), während Lesezugriffe den aktuellen Schnittstellenstatus liefern. Die einzelnen Bits sind dabei wie folgt definiert:

Bit 0 Printer: Acknowledge Bit 1 Printer: Paper Empty

Bit 2 Printer: Error Bit 3 Printer: Select

Bit 4 IDE-Platte: Interrupt Request

Bit 5 Printer: Busy

Bit 6 Interface: Strobe Delay

Bit 7 Interface: Composed Busy

Beim Pollen des Schnittstellenstatus vor dem Senden von Zeichen ist Bit 7 (Composed Busy) zu verwenden (0 = Schnittstelle bereit).

# 86h IDE-Platte Digital Output Register 87h IDE-Platte Zweitstatus-Register

Diese beiden Register sind nicht zwingend vorhanden bzw. bei verschiedenen Festplatten unterschiedlicher Hersteller identisch verwendet. Vor dem Benutzen dieser Register ist unbedingt das Handbuch der jeweiligen Festplatte zu studieren! (Bei PC/AT's liegen diese Register normalerweise auf den Adressen 3F6h und 3F7h.)

88h IDE-Platte Datenregister

89h IDE-Platte Fehlerregister

8Ah IDE-Platte Sektorzähler

8Bh IDE-Platte Sektornummer

8Ch IDE-Platte Zylindernummer Low

8Dh IDE-Platte Zylindernummer High

8Eh IDE-Platte Laufwerksnummer und Kopf

8Fh IDE-Platte Befehls-/Statusregister

Diese acht Register sind die Arbeitsregister für Zugriffe auf IDE-Festplatten. Die Inhalte der einzelnen Register sind i.A. auch bei verschiedenen Festplattentypen und -herstellern identisch (entsprechend dem sog. Industriestandard). Allerdings kann es bei einzelnen Bits sowie bei den unterstützten Befehlscodes Differenzen geben, so daß auch hier das Studium des Festplattenmanuals unbedingt zu empfehlen ist. (Bei PC/AT's liegen diese Register auf den Adressen 1F0h bis 1F7h.)